Logic Circuits 101: Understanding Combinational Logic and Its Applications

A beginner-friendly guide to the principles and practical uses of combinational logic circuits

Combinational Logic Circuits are memoryless digital logic circuits whose output at any instant in time depends solely on the combination of its inputs.

• These circuits are constructed from basic logic gates like NAND, NOR, or NOT. These gates are “combined” or connected together to form more complex switching circuits.

• The output of Combinational Logic Circuits is determined only by the current state of the inputs (logic “0” or logic “1”) at any given moment, not by any previous states or history.

• For a logic circuit to be classified as combinational, it must meet two conditions:

Every component within the circuit must be combinational.

The circuit must not have any cyclic paths (i.e., no feedback loops).

• While Combinational Logic Circuits are conceptually simple, they can become quite intricate. They can be represented using three methods:

Boolean Algebra - Mathematical representation of logic circuits.

Truth Table - A tabular representation showing all possible input combinations and their corresponding outputs.

Logic Circuit Diagram - A visual representation of the circuit showing the arrangement of logic gates.

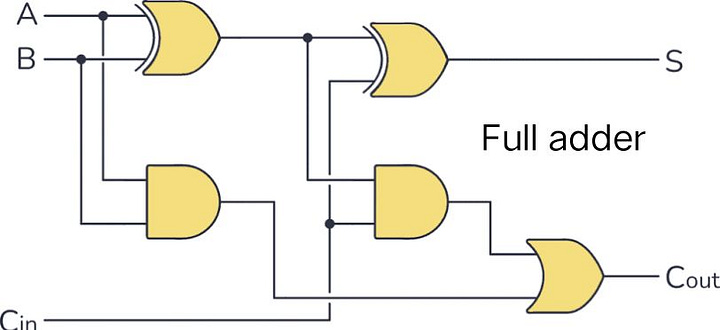

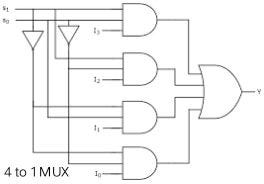

• These circuits are fundamental in various applications such as arithmetic operations, data transmission, and logical functions. Examples include Adders, Subtractors, Multiplexers, and Decoders. For instance, a 4-input 1-output Multiplexer and a Full Adder are common examples of combinational logic circuits.

• Interested in exploring Verilog implementations? Check out my GitHub repository for practical Verilog code and examples of combinational logic circuits. Explore Verilog Code on GitHub.

• Stay tuned for more posts! I will cover various combinational logic circuits, including their Verilog code and possibly implementation on FPGA boards, in the upcoming weeks.

Connect with Me:

LinkedIn: Rana Umar Nadeem

Medium: @ranaumarnadeem

GitHub: ranaumarnadeem/HDL

Substack: We Talk Chips